ZYNQ SATA Storage Extension for the Xilinx ZC706

This Technical Brief shows how to setup the Zynq SSE. After going through the steps described herein, you will have a working Linux System running on the Zynq with an attached SATA HDD or SSD.

Copyright © 2026 Missing Link Electronics. All rights reserved. Missing Link Electronics, the stylized Missing Link Electronics MLE logo are the service mark and/or trademark of Missing Link Electronics, Inc. All other product or service names and trademarks are the property of their respective owners.

For the evaluation of Zynq SSE MLE supports two separate hardware platforms: The Avnet Zynq Mini-ITX board, and the Xilinx ZC706 Development Kit plus the XM104 Adapter Board. This document is for the Xilinx ZC706 plus the XM104 Adapter Board.

The Zynq SATA Storage Extension (Zynq SSE) is a fully integrated and pre-validated system stack comprising 3rd-party SATA Host Controller and DMA IP cores from ASICS World Services, a storage micro-architecture from MLE, Xilinx PetaLinux, and an Open Source SATA Host Controller Linux kernel driver, also from MLE. Zynq SSE utilizes the Xilinx GTX Multi Gigabit Transceivers to deliver SATA I (1.5 Gbps), SATA II (3.0 Gbps), or SATA III (6 Gbps) connectivity.

The Zynq SSE is delivered as a complete reference design for the Xilinx Zynq-7000 All Programmable SoC (Zynq), and effectively extends Zynq with one single SATA host port for HDD and SSD storage connectivity.

This Technical Brief shows how to setup the Zynq SSE. After going through the steps described herein, you will have a working Linux System running on the Zynq with an attached SATA HDD or SSD.

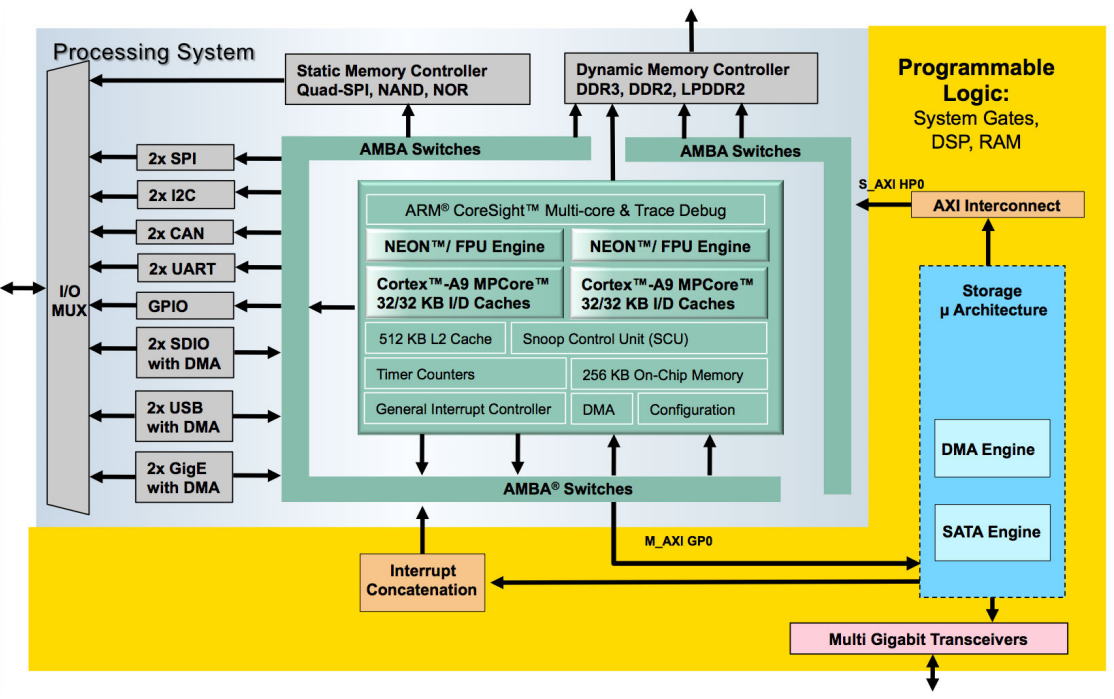

Block Diagram

The block diagram shown below gives an overview over the Zynq SSE reference design: Within the Zynq Programmable Logic (PL) the MLE storage micro-architecture instantiates the DMA and the SATA Host Controller IP blocks. The storage micro-architecture itself interfaces with the Zynq Processing System (PS) via the high-performance AXI HP0 slave port. The ARM A9 in the PS runs Xilinx PetaLinux and the SATA Linux kernel driver.

Implementation

| Implementation Details | |

|---|---|

| Design Type | PS + PL |

| SW Type | Linux (Petalinux) |

| CPUs | 2 CPUs 700 MHz |

| PS Features | DDR, USB, UART, ETHERNET |

| PL Cores | ASICS.WS SATA IP |

| Boards/Tools | ZC706, XM104 |

| Xilinx Tools Version | Vivado 2014.1, PETALINUX 2013-2 |

| Other Details | Samsung 840 SSD(including Cable and Power Supply), SD-Card |

| Address Map | |||

|---|---|---|---|

| Base Address | Size | Interface | |

| SATA IP | 0x41000000 | 4K | S AXI |

| DMA IP | 0x41010000 | 4K | S AXI, M AXI |

| Files Provided | |

|---|---|

| BOOT.bin | Compilation of Bitstream, FSBL and U-Boot |

| Image.ub | Linux Ramdisk Image |

Step by Step Instructions

Hardware needed

- ZC706 Board (including Power supply)

- XM104 FMC Board

The XM104 Adapter Card is available from Avnet:

http://www.em.avnet.com/en-us/design/drc/Pages/Xilinx-FMC-XM104-Connectivity-Card.aspx - Mini USB Cable for USB Console

- Supported SSD (for Example Samsung 840)

- Power Supply for SSD

- SD Card (2 GB or bigger)

- PC for UART console and Ethernet

Software Assembly

- Format the SD Card using FAT32 File system

- Put image.ub and BOOT.bin into the root directory of the SD Card

Hardware Assembly

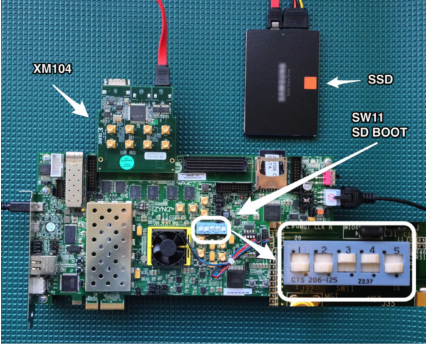

- Insert the SD Card into the ZC706 SD Slot

- Connect the XM104 card to the HPC Port of the ZC706

- Connect the mini USB cable to the UART port of the ZC706 and the USB Port of your PC

- Connect the SSD to the XM104 SATA 1 port using the SATA Cable

- Connect the SSD to power

- Switch the ZC706’s SW11 to SD Boot mode (as shown in picture)

- Connect the ZC706 to the Power Supply

The system should now look like in the supplied image

Startup

- Switch on the ZC706

- On the PC open a Serial Terminal on the new serial port using the settings 115200 Baud 8N1

- Observe the Linux System booting

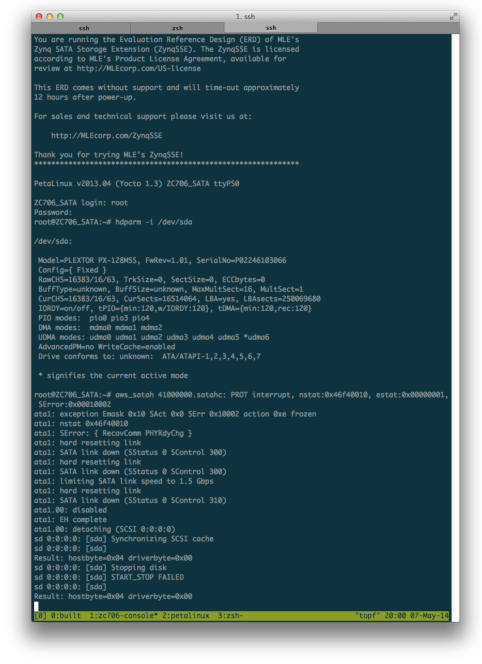

- After some time you should see a screen similar to the screenshot in the Expected Results

- Login using

- Login:root

- Password: root

LED Description

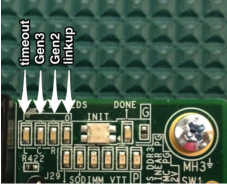

Status LEDs can be found in the upper right corner of the board, next to the power switch. The associated meanings can be seen in the following table and in the Image below.

| GPIO LED LEFT | Timeout LED, indicates the Timeout of the IP core. |

| GPIO LED CENTER | Gen3 Link, indicates 6 GBit/s connection |

| GPIO LED RIGHT | GEN2 Link, indicate 3 GBit/s connection |

| GPIO LED 0 | Linkup and Activity |

Expected Results

As a result you should be having a running Linux system on the Zynq board. The UART Console output should be similar to the screenshot below.

Also you will have file-system access to the attached SSD using FTP, and by this evaluate and test the Zynq Sata Storage extension.

The Evaluation Reference Design (ERD) of the Zynq SSE comprises a hardware license management which allows to run full SATA functionality for up to 12 hours after power-up. After approximately 12 hours the evaluation expires, which is indicated by illuminating the LED ’timeout’. You will also notice that the Linux kernel driver informs you of having lost the SATA link to the SSD/HDD.

Team MLE has spent significant efforts to try and test all aspects of Zynq SSE. If you feel that you encounter something not right, or if you do have any questions, please do not hesitate to contact us.

🌐 www.missinglinkelectronics.com

MLE (Missing Link Electronics) is offering technologies and solutions for Domain-Specific Architectures, which focus on heterogeneous computing using FPGAs. MLE is headquartered in Silicon Valley with offices in Neu-Ulm and Berlin, Germany.